먼지 쌓인 키보드

[정보처리기사 필기] 전자 계산기 정리 본문

=========전자계산기===========

· write-through : 쓰기 동작이 이루어질때마다 캐시 메모리와 주기억장치의 내용을 동시에 갱신

· DMA (*중요*)

: 입출력장치가 직접 주기억장치를 접근하여 Date Block을 입출력하는 방식으로 cpu의 레지스터를 경유하지 않고 수행, 빠른 데이터 전송

인터럽트 신호발생해 입출력 종료 알림, cycle steal 방식 이용(*중요*), 메모리와 버스 공유

(하나의 제어기로 여러 종류 I/O장치 제어: 채널)

· DMA 제어기의 구성요소

- 인터럽트 회로 : 입출력장치와 통신 담당

– 주소 레지스터 : 위치지정위한 번지기억및전송

- 제어 레지스터 : 전송 방식 결정

– 데이터 레지스터 : 자료나 주소 임시 기억

– 워드 카운터 레지스터 : 워드의 수 기억

· I/O프로세서 : DMA제어기의 한계 극복

· I/O 제어 방식: Program에 의한, Interrupt에 의한, DMA에 의한, Channel에 의한(비동기 데이터 전송 : 스트로펄스(Strobe Pulse), 핸드셰이킹(Handshaking))

· 다중포트메모리 : 다중처리기 상호 연결 방법 중 하나의 프로세서에 하나의 버스가 할당되어 버스를 이용하려는 프로세서간 경쟁이 적은 것

· Gray 코드

- BCD 코드의 인접하는 비트를 XOR연산 하여 만든 코드

- 비가중 코드

- 입출력 장치, A/D 변환기, 주변장치 등에서 순자를 표현할 때 사용

- 1Bit만 변환 시켜 다음 수치로 증가시키기 때문에 하드웨어적인 오류가 적다

· Gray Code -> 2진 코드 변환

1) 2진수의 첫 번째는 그대로 내려 씀

2) 두 번째 2진수 비트부터는 왼쪽에 구해 놓은 2진수 비트와 변경할 해당 번째 그레이 비트를 XOR연산하여 쓴다

· 2진 코드 -> Gray Code 변환

1) 그레이 코드의 첫 번째는 그대로 내려 씀

2) 두 번째 그레이 비트부터는 변경할 2진수의 해당 번째 비트와 그 왼쪽 비트를 XOR 연산

· 채널

- 고정 채널 : 채널 제어기가 특정한 I/O 장치들에 전용인 전송통로를 지닌 형대, 구성 간단, 가변채널에 비해 효율 낮음

- 버스트 모드 : 하나의 I/O 장치가 데이터 전송을 행하고 있는 동안에는 채널의 기능을 완전히 독점, 대량 데이터 고속 전송

- 멀티플렉서 채널 : 여러 개의 I/O 장치가 채널의 기능을 공유하여 시분할적으로 데이터를 전속하는 형태, 여러개 동시에 동작

- 블록 멀티플렉서 채널 : 하나의 데이터 경로, 고속이 입출력 장치, 바이트 멀티플렉서와 Selector 채널을 결합한 형태

· Bandwidth(대역폭, 전송률) : 메모리로부터 또는 메모리 까지 1초 동안 전송되는 최대한의 정보량, 기억장치의 자료 처리 속도를 나타냄, 물리적으로 버스의 크기에 영향을 받음

-정보전달 능력의 한계

· 디스크 저장장치 용량 : 디스크개수 X 디스크당 면수 X 디스크당 트랙수 X 트랙당 섹션수 X 섹터당 용량 (byte*1024=KByte)

·(*중요*)

RAID-5는 RAID-4의 패리티 디스크의 액세스 집중 문제를 해결하기 위해 개발

· 블루레이 디스크·(*중요*)

- 파란색 레이저를 사용

- 비디오 포맷은 DVD와 동일한 MPEG-2 기반 코덱이 사용

- 단층 기록면을 가지는 12cm 직경에 25GB의 데이터를 저장

- 기술 규격으로 DB-ROM(읽기전용), DB-R(기록가능), DB-RE(재기록 가능)가 있다.

플립플롭 종류(*중요*)

· SR플리플롭

0 0 = 유지, 0 1 = 0 , 1 0 = 1 , 1 1 = 금지

· JK플리플롭

0 0 = 유지, 0 1 = 0 , 1 0 = 1 , 1 1 = 보수

· D플리플롭(*중요*)

기존 상태와 상관없이 입력된 값을 그대로 저장

입력한 값을 그대로 저장

· T플리플롭

0이 입력되면 기존의 상태 그대로 저장

1이 입력되면 기존의 상태의 보수

(*중요*)

· PC와 MAR = 워드의 개수(2^n에서 n) =주소선

MBR = 워드의 크기

워드의 개수 = 용량 / 워드 길이

MAR과 MBR구하는 것(*중요*)

용량 N 이라면 2^n = N이 되는걸 찾음

MAR = n

MBR = 워드의 길이

· 윈체스터 디스크 : 자기 디스크에 헤드가 가까울수록 불순물이나 결함에 의한 오류 발생의 위험이 더 크다. 이 문제점을 해결한 것

· 연산자의 기능

- 함수 연산 기능 : 산술연산(ADD, SUB, MUL, DIV, 산술 shift)과 논리 연산(NOT, AND, OR, XOR, 논리적 Shift, Rotate, Complement, Clear 등)

- 자료 전달 기능 : CPU와 기억장치 사이에서 정보를 교환하는 기능(Load, Store, Move, Push, Pop)

- 제어 기능 : 실행 순서를 변경시키는 기능(GOTO, Jump, IF, SPA, SNA, SZA, Call, Return)

- 입/출력 기능 : CPU와 I/O 장치 또는 메모리와 I/O 장치 사이에서 자료를 전달하는 기능(INPUT, OUTPUT)

ADD***중요

MAR <- MBR(ADDR)

MBR <- M(MAR)

EAC <- AC + MBR

LOAD (*중요*)

MAR <- MBR(ADDR)

MBR <- M(MAR), AC <- 0

AC <- AC + MBR

· 데이터 흐름형 컴퓨터(date flow machine)

: 프로그램 내의 모든 인스트럭션이 그들의 수행에 필요한 피연산자들이 모두 준비되었을 때 그 인스트럭션을 수행하는 것으로 데이터 추진 방식

· 플린의 병렬 컴퓨터 분류***중요

SISD : 한 개의 명령, 한 개의 자료 처리

SIMD : 한 개의 명령, 여러개 자료 처리

MISD : 여러개의 명령, 한 개의 자료 처리

MIMD : 여러개의 명령 여러개의 자료 처리

인터럽트의 요청이 있을 때 처리 내용(*중요*)

-PSW에 현재의 상태를 보관

-인터럽트를 요구한 자이를 위한 인터럽트 서비스 프로그램을 실행

-인터럽트 시버스 프로그램은 실행하는 중간에 다른 인터럽트를 처리할 수 있음(*중요*)

· 주요 연산자의 기능

- AND(Masking Operation) : 특정 비트 삭제, 0비트를 마스크 비트라 함

- OR(Selective-Set) : 특정 문자 삽입, 특정 비트 1

- XOR(Compare, 비교)***중요 : 2개의 데이터를 비교, 특죽정 비트 반전, 반전 시킬시 1과 XOR

(NAND gate 5개로 만들거나, NOR gate 5개)

- NOT(Complement, 보수) : 값을 반전

- 논리 Shift : 왼쪽 오른쪽 1Bit씩 자리 이동, 데이터의 직렬 전송, 삽입 되는 자리 무조건 0

- Rotate : Shift에서 밀려 나가는 비트의 값을 반대편 값으로 입력, 문자 위치 변환

- 산술 Shift(*중요*) : 왼쪽->*2^n, 오른쪽->/2^n, 홀수를 오른쪽 한번->0.5 오차 발생 (특수한 곱셈과 나눗셈을 수행되고 보조적으로 이용)

· 주요 레지스터의 종류 및 기능

- 프로그램 카운터, 프로그램 계수기(PC) : 다음번에 실행할 명령어의 번지를 기억

- 명령 레지스터(Instruction Register) : 현재 실행 중인 명령의 내용을 기억

- 누산기(Accumulator) : 연산 된 결과를 일시적으로 저장

- 상태 레지스터(Status Register), PSWR(Program

Status Word Register), 플래그 레지스터 : 시스템 내부의 순간순간의 상태가 기록된 정보를 PSW라 함, 오버플로, 언더플로, 자리올림, 인터럽트 등의 PSW를 저장

- 메모리 주소 레지스터(MAR) : 기억장치를 출입하는 데이터의 번지를 기억

- 메모리 버퍼 레지스터 : 기억장치를 출입하는 데이터가 잡시 기억

- 인덱스 레지스터 : 주소의 변경이나 프로그램에서의 반복연산의 횟수를 세는 레지스터

- 데이터 레지스터 : 연산에 사용 될 데이터를 기억

- Shift Register : 저장 된 값을 1Bit씩 오른쪽이나 왼쪽으로 이동, 2배 길이 레지스터라고 함

- 메이저 스테이터스 레지스터 : CPU의 메이저 상태를 저장

· 부동 소수점인 두 수의 나눗셈

1) 0 인지의 여부를 조사

2) 레지스터를 초기화시키고 부호를 결정한다

3) 피젯수를 위치 조정한다

4) 지수의 뺄셈을 한다

5) 가수의 나눗셈을 한다

· CISC(complex)와 RISC(reduce) 비교

|

구분 |

명령어 |

주소지정 |

레지스터 |

전력소모 |

처리속도 |

용도 |

|

RISC |

적음 |

간단 |

많음 |

적음 |

빠름 |

서버,워크스테이션 |

|

CISC |

많음 |

복잡 |

적음 |

많음 |

느림 |

개인PC |

· 인터럽트와 비교하여 DMA방식에 의한 사이클 스틸의 가장 특징적인 차이점 : 주기억장치 사이클의 한주기만 정지

· 마이크로 오퍼레이션 (*중요*)

- instruction을 수행하기 위해 CPU 내의 레지스터와 플래그가 의미 있는 상태 변환을 하도록 하는 동작

- 레지스터에 저장된 데이터에 의해 이루어짐

- 한 개의 Clock 펄스 동안 실행되는 기본 동작

- 컴퓨터의 모든 명령을 구성하고 있는 몇가지 종류의 기본 동작

- 제어장치가 발생하는 신호 -> 제어 신호

- 한 개의 Instruction은 여러 개의 Mico Operation이 동작되어 실행

· 크로스 어셈블러(*중요*) : 현재 사용하는 컴퓨터와는 다른 명령 형태로 동작하는 컴퓨터에서 사용 할 수 프로그램을 어셈블 할 때 사용 되는 어셈블러, 목적 프로그램을 생성

· 주소 지정 방식 (*중요*)

- 암시적 주소지정 방식(Implied Mode) : 주소를 지정하는 필드가 없는 0번지 명령어에서 Stack의 Top 포인터가 가르키는 Operand를 암시

- 즉치(즉시)적 주소지정 방식(Immediate Mode) : 명령어 자체에서 실제 데이터를 가지고 있는 방식, 실행 속도가 빠름

- 직접 주소지정 방식(Direct Mode) : 명령어의 주소부에 있는 값이 실제 데이터가 기억된 번지를 지정하는 방식

- 간접 주소지적 방식(Indirect Mode) : 명령어의 주소부가 지정하는 곳에 있는 값이 실제 데이터를 기억하는 또 다른 메모리의 번지를 지정하는 방식, 최소한 두 번 이상 접근ddds

· 마이크로프로그램 제어기가 다음에 수행할 마이크로인스트럭션의 주소를 결정하는데 사용하는 정보는 인스트럭션 레지스터, CPU상태 플러그, 마이크로 인스트럭션에 나타난 주소이다.

· 인스트럭션의성능=수행시간/패치시간+준비시간

·스택인스트럭션은 다른 명령어 형식에 비해 수행시간이 짧다

***중요***중요

· 디코더 : n개의 input line

2^n개의 출력선

중앙처리장치 내에서 번지의 해독, 명

령의 해독, 제어 등에 사용

인코더 : 2^n개의 input line

n개의 출력선

멀티플렉서 : 2^n개의 input line

n개의 selection line

1개의 출력선

디멀티플렉서 : 1개의 input line

n개의 selection line

2^n개의 출력선

· SSD

- SLC(single Level Cell) : 셀 당 1비트

- MLC(Multi Level Cell) : 셀 당 2비트

- TLC(Triple Level Cell) : 셀 당 3비트

· 입출력 제어장치의 종류(*중요*)

: DMA, 채널, 입출력 프로세서

·메모리 인터리빙(*중요*) : 중앙처리장치의 기억 모듈에 중복적인 데이터 접근을 방지하기 위해서 연속된 데이터 또는 명령어들을 기억장치모듈에 순차적으로 번갈아 가면서 처리하는 방식(대역폭늘림)

-단위 시간에 여러 메모리의 접근이 가능하도록 하는 방법

-캐시 기억장치, 고속 DMA 전송 등에서 많이 사용

-기억장치의 접근 시간을 효율적으로 높임

-각 모듈의 번갈아 가면서 접근

· 버스 사용 우선 순위(*중요*)

- 회전 우선순위(Rotating Priority)

(모든 마스터들이 한단계씩 낮아지고, 가장 낮았던 우선순위가 최상위 우선순위를 가짐)

- 임의 우선순위(Random Priority)

(닌스 발생기의 의해 우선순위가 정해짐)

- 동등 우선순위(Equal Priority)

(동등한 우선순위나, FIFO알고리즘 사용하여, 먼저 도착한 요구를 먼저 승인)

- 최소-최근 수선순위(Least0recently used)

(최근 가장 오랫동안 사용하지 않은 마스터에게 최상위 우선순위 할당)

· 해밍코드 계산법

- 짝수면 0, 홀수면 1

1) 1, 2, 4 비우고 나머지 정보 비트 기입

2) 3, 5, 7 비교해서 짝순지 홀수인지 ->1에 기입

3) 3, 6, 7 비교해서 짝순지 홀수인지 ->2에 기입

4) 5, 6, 7 비교해서 짝순지 홀수인지 ->4에 기입

· 배열처리기 : PE라 불리는 복수개의 산술, 논리연산장치를 갖는 프로세서로 동기적으로 병렬처리를 수행하고 동시에 같은 기능을 수행하는처리기

·플리플롭은 전력이 공급되고 있는 한 상태의 변화를 위한 신호가 발생할 때까지 현재상태를 그대로 유지하는 논리회로

레지스터를 구성하는 기본 소자

기억기능을 가짐

·CPU메이저상태 (*중요*)

-Fetch(인출) : 주기억장치에서 중앙처리장치의

명령 레지스터로 가져와 해독하는 단계

-Indirect(간접) : 해석된 명령의 주소부가 간접주

소인 경우 수행, 유효주소구함

MAR <- IR(addr)

MBR <- memory or register

IR <- MBR(addr)

-Excute(실행) : 해석한 명령을 시행하는 단계

-Interrupt (*중요*):

하드웨어로 실현되는 서브루틴호출

·인터럽트의 종류 (*중요*)

- 외부 인터럽트

전원이상: 정전, 전원이상

기계착오 : cpu기능적오류발생

외부신호 : 타이머, 키보드, 외부장치

입출력 : 입출력데이터 오류나 이상현상

- 내부 인터럽트

잘못된명령,데이터 사용할 때 (=트랩)

0으로 나누거나 overflow,underflow 발생

- 소프트웨어 인터럽트

SVC : 사용자가 SVC명령 사용해 의도적 호출

(명령의 요청에 의해 발생하는 대표적 인터럽트)

· 자기 테이프

- 순차처리 대용량저장매체 // 랜덤처리X

- 가격이 저렴, 용량커서 백업용

- 7-9bit 동시에 수록되고 전달

- 각블록 사이에 물리적 래코드 존재

- sequential access가 가능

· 블로킹 장점 : 기억공간의 낭비 줄고 access time 감소, 입출력 횟수가 감소

· 고정배선제어장치와 마이크로프로그래밍

|

구분 |

고정배선 제어장치 |

마이크로 프로그래밍 |

|

반응속도 |

고속 |

저속 |

|

회로복잡도 |

복잡 |

간단 |

|

경제성 |

비경제적 |

경제적 |

|

융통성 |

없음 |

있음 |

|

구성 |

하드웨어 |

소프트웨어 |

· 프로그램을 통한 입출력 방식에서 입출력장치 인터페이스가 포함되어야 하는 하드웨어

- 데이터 레지스터

- 장치의 동작 상태를 나타내는 플래그

- 장치번호 디코더

·파이프라인은 여러개의 명령을 동시에 병렬 처리하는 장치로 cpu프로그램 처리속도를 개선

- 파이프라인을 차고 나면 연속적인 결과를 얻을 수 있으므로 연산 속도가 빠름

- 같은 연산이 여러번 반복되어 사용되면 효율적 그렇지 않으면 구조 복잡하고 시간 오래걸림

· 명령어 파이프라인이 정상적인 동작에서 벗어나게 하는 원인은 자원충돌, 데이터의존성, 분기곤란

·사상(mapping)(*중요*) : 가상주소를 실주소로, 데이터의 논리적 구조를 물리적구조로, 매크로 동작을 마이크로 명령어 주소로 변환하는 작업을 할 때 사용하는 기법

(매핑 프로세서의 종류 : 직접 매핑, 어소시에이티브 매핑, 세트-어소시에이티브 매핑)

-주소로부터 기억 장소로의 변환에 사용

· 메가플롭스(MFLOPS)**중요 : 1초에 실행되는 부동소수점 연산의 수를 100만을 단위로 하여 나타 냄

· 기가플롭스(GFLOPS)**중요 : 1초에 실행되는 부동소수점 연산의 수를 10억 번 수행

· IEEE 754 부동 소수점 표현에는 부호(Sign), 지수(Biased Exponent), 가수부(Fraction)으로 표현

· 중앙처리장치의 구성요소 : 제어, 연산, 레지스터, 버스 (레지스터-IR, MAR, PC)

· 주소 설계시 고려 사항(*중요*)

- 표현의 효율성 – 사용의 편리성

- 주소 공간과 기억 공간의 독립성

- 수행속도가 증가될 수 있도록함

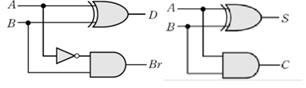

· 조합논리회로 : 반가산기, 전가산기, 병렬가산기, 반감산기, 전감산기, 디코더, 인코더, 멀티플렉서, 디멀티플렉서, 다수결회로, 비교기

반가산기, 반감산기, 가산기, 감산기*중요

반감산기 반가산기

· 순서논리회로 : 플리플롭, 카운터, 레지스터, RAM, CPU 등

· 동적램 (DRAM) / 정적램 (SRAM)**중요

|

|

DRAM |

SRAM |

|

구성소자 |

콘덴서 |

플리플롭 |

|

특징 |

주기적 재충전 |

전원공급동안 기억내용 유지 |

|

전력소모 |

적음 |

많음 |

|

접근속도 |

느림 |

빠름 |

|

집적도(밀도) |

높음 |

낮음 |

|

가격 |

저가 |

고가 |

|

용도 |

일반적 주기억장치 |

캐시메모리 |

DRO(Destructive Read Out)(*중요*)-파괴적 읽기

DRAM(*중요*) – 비파괴적 읽기

· 연관기억장치(Associative Memory)=CAM(*중요*)

기억장치에서 찾을 때 주소에 의해 접근하지 않고 기억된 내용의 일부를 이용하여 접근하는 기억장치

- 정보 검색이 신속 (병렬) (시간 절약)

- Mapping Table에 사용

- 하드웨어 비용이 증가 (DRAM보다 비쌈)

- 명령어를 랜덤하게 기억

- 구조 및 동작이 복잡

- 저장된 정보에 대해 주소보다 내용의해검색

· 인터럽트 서비스 루틴의 기능

- 처리기 상태 복구

- 인터럽트 원인 결정

- 처리기 레지스터 상태 보존

- 상대적으로 낮은레벨의 마스크 레지스터클리어

· 클러스터(cluster) : 여러 대의 상호 독립적인 동작이 가능한 컴퓨터들이 연결된 전체 컴퓨터들의 집합으로, 전체 컴퓨터들이 상호 연결되어 협력하면서 하나의 컴퓨팅 자원인 것처럼 동작

· 디지털 IC의 성능 평가 요소

- 전파 지연 시간, 전력 소모, Fan out, 잡음 허용치

· 폴링***중요 : 소프트웨어에 의하여 인터럽트의 우선순위 판별하는 방법, 인터럽트 요청 신호 플래그를 차례로 검사하여 인터럽트의원인을판별하는 방식

폴링 특징***중요(*중요*)

-비교적 큰 정보를 교환하는 시스템에 적합

-융통성이 있음

-반응속도 느림

우선순위 판별 결정 방법·(*중요*)

-폴링

-벡터

-데이지 체인

· 하드웨어적인 인터럽트 판별 방식

vectored interrupt(*중요*) - 특정 번지 서브루틴

· (*중요*)직렬 우선순위 부여 방식

= (*중요*)데이지 체인 방식)

· 기억장치별 접근 속도 (빠름->느림)

cpu 레지스터 -> cache -> ram -> rom -> 자기코어 -> 자기디스크 -> 자기테이프

// 마이크로 사이클 타임 부여 방식

· 동기 고정식(*중요*)

- 모든 마이크로 오퍼레이션의 동작시간이 같다고 가정하여 cup clock 주기를 마이크로 사이클 타임과 같도록 정의 (동작시간 비슷할 때 유리)

- 마이크로 오퍼레이션 중 동작시간이 가장 긴 마이크로 오퍼레이션 동작시간을 마이크로 사이클 타임으로 정의

· 동기 가변식(*중요*)

- 수행시간이 유사한 마이크로 오퍼레이션끼리 그룹을 만들어 각 그룹 별로 서로다른 마이크로 사이클 타임을 정의

- 마이크로 오퍼레이션 수행시간이 현저한 차이 날 때 사용

- 각 집합간 서로 다른 사이클 타임의 동기를 맞추기 위하여(*중요*) 집한간의 마이크로 사이클 타임을 정수배(*중요*)가 되도록 한다.

· 비동기식**중요

- 모든 마이크로 오퍼레이션에 대하여 서로 다른 마이크로 사이클 타임을 정의하는 방식

· 정수의 표현 범위***중요

|

종류 |

범위 |

|

부호화 절대치법 |

-2^(n-1)+1 ~ 2^(n-1)-1 |

|

부호화 1의 보수법 |

|

|

부호화 2의 보수법 |

-2^(n-1) ~ 2^(n-1)-1 |

1의 보수와는 다른 2의 보수의 특징

-음수화 구현이 쉽다

-연산과정이 간단

-0이 하나

· 산술 shift (음수에서, 양수는 모두 0)

shift left : 부호화 절대치 : padding bit = 0

1의 보수법 : padding bit = 1

2의 보수법 : padding bit = 0

shift right : 부호화 절대치 : padding bit = 0

1의 보수법 : padding bit = 1

2의 보수법 : padding bit = 1

· 채널 명령어 알 수 있는 내용 :명령코드, 데이터주소(블록시작주소), 데이터크기(블록의단어수), 플래그(채널의 링크주소)

· 명령어 형식***중요

3-주소 명령어 : Operand부가 3개로 구성되는 명령어 형식으로 여러 개의 범용 레지스터를 가진 컴퓨터 사용, 결과는 Operand1에 기록

2-주소 명령어 : Operand부가 2개로 구성되는, 가장 일반적으로 사용되는 명령어 형식으로 여러 개의 범용 레지스터를 가진 컴퓨터에 사용(MOVE)

1-주소 명령어 : Operandq가 1개로 구성되어 있으며, 1-주소 명령어 형식의 컴퓨터는 누산기(AC, Accumulator)를 이용하여 명령어 처리

( 명령어 MULA : AC <- AC * M[A] )

0-주소 명령어 : Operand부 없이 OP-Code부만으로 구성되어 있으며, 모든 연산은 Stack 메모리의 Stack Pointer가 가리키는 Operand를 이용하여 수행함(PUSH/POP)

명령어의 구성 중 주소(Operand)부(*중요*)

- 기억장치의 주소

- 레지스터 번호

- 사용할 데이터

· 사이클 스틸(Cycle Steal)(*중요*)

- 데이터 채널과 CPU가 주기억장치를 동시에 Access할 때 우선순위를 데이터 채널에 넘겨주는 방식

- 한 번에 한 데이터 워드 직접 전송

- 버스의 제어를 CPU에게 돌려 줌

- 입출력 자료의 전송을 빠르게 처리

· 마스터-슬레이브 플립플롭(주종)

- 출력 측의 일부가 입력 측에 궤환 되어 유발하는 레이스 현상을 없애기 위해 고안

- 2개의 플립플롭으로 구성

- 한쪽이 마스터 나머지가 슬레이브

· 인스트럭션 세트 설계 시 고려 사항(*중요*)

- 연산자의 종류

- 주소 지정 방식

- 데이터구조

- 명령어 형식

- 사용빈도 및 기억 공간

- 주기억장치 밴드폭 이용

인스트럭션 주소 결정시 사용하는 정보(*중요*)

-인스트럭션 레지스터(IR)

-CPU의 상태 레지스터

-마이크로 인스트럭션에 나타난 주소

· 디코더 : Code화 된 정보 -> 2^n 변역 회로

· 인코더 : 디코더의 반대

· 간접 주소 방식의 특징

- 명령의 길이가 짧고 제한되어 있어도 긴 주소에 접근 가능한 방식

- 최소한 주기억 장치를 두 번 이상 접근 해야 도달

· 입출력에 필요한 하드웨어의 기능 : 입출력 제어기, 입출력 인터페이스, 입출력 버스

· 가상 기억장치의 궁극적인 목적 : 용량의 확대

BASIC(*중요*) : 언프리터를 사용하는 언어

논리회로(*중요*)

A AND B = A*B

A OR B = A+B

______

A NAND B = A*B

_____

A NOR B = A+B

______ _ _

A*B = A + B

_____ __ __

A+B = A * B

AND A*B

-특정 문자 또는 특정 비트를 삭제시키는 연산

OR A+B

-특정 문자를 삽입할때

_

NOT A

-보수를 구할때

_ _

XOR A⊕B = AB + AB

-비교할때

selective 연산 : OR

MASK 연산 : AND

(*중요*)다음과 같은 값을 가지는 시스템에서 2계층 캐시 메모리를 사용할 경우는 그렇지 않은 경우에 비해 평균 메모리 액세스 시간이 약 몇 배 향상되는가?

L1 히트시간 = 1사이클

L1 미스율 = 5%

L2 히트시간 = 4사이클

L2 미스율 = 20%

L2 미스 패널티 = 100사이클

메모리 액세스 시간(2계층 사용X)

= L1히트시간 + L1미스율 * L2미스패널티

1+ 0.05*100 = 6

L1 미스패널티

= L2히트시간 + L2미스율 * L2미스 패널티

= 4 + 0.2 *100 = 24

메모리 액세스 시간(2계층 사용)

= L1히트시간 + L1미스율 * L1미스패널티

= 1 + 0.5 * 24 = 2.2

6 / 2.2 = 2.73배 약 2.7배 향상

(*중요*)

전체 기억장치 액세스 횟수가 50이고, 원하는 데이터가 캐시에 있는 횟수가 45라고 할 때, 캐시의 미스율(miss ratio)_은?

캐시의 미스율 = 1 - H

원하는 데이터 횟수 = 45

전체 기억장치 액세스 횟수 = 50

H = 45/50 = 0.9

1 – H = 1 – 0.9 = 0.1

마쉐링(Marshalling)(*중요*)

-하나 이상의 프로그램 또는 연속되어 있지 않은 저장 공간으로부터 데이터를 모은 다음, 데이터들을 메시지 버퍼에 넣고, 특정 수신기나 프로그래밍 인터페이스에 맞도록 그 데이터를 조직화 하거나 미리 정해진 다른 형식으로 변환하는 과정

'공부 관련 > 정보처리기사' 카테고리의 다른 글

| [정보처리기사 필기] 1~5과목 이것만은 외우고 시험가자 (0) | 2019.02.26 |

|---|---|

| [정보처리기사 필기] 데이터 통신 정리 (0) | 2019.02.26 |

| [정보처리기사 필기] 소프트웨어공학 정리 (0) | 2019.02.26 |

| [정보처리기사 필기] 운영체제 정리 (0) | 2019.02.26 |

| [정보처리기사 필기] 데이터베이스 정리 (0) | 2019.02.26 |